# MPLAB<sup>®</sup> ICE 4000 IN-CIRCUIT EMULATOR USER'S GUIDE

© 2004 Microchip Technology Inc.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net. PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2004, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

# **QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV**

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# MPLAB<sup>®</sup> ICE 4000 USER'S GUIDE

# **Table of Contents**

| Preface                                                             | . 1 |

|---------------------------------------------------------------------|-----|

| Chapter 1. Overview                                                 |     |

| 1.1 Introduction                                                    | . 7 |

| 1.2 Highlights                                                      | . 7 |

| 1.3 MPLAB ICE 4000 Defined                                          | . 7 |

| 1.4 How MPLAB ICE 4000 Helps You                                    | . 7 |

| 1.5 MPLAB ICE 4000 Kit Components                                   | . 8 |

| Chapter 2. Installation                                             |     |

| 2.1 Introduction                                                    | . 9 |

| 2.2 Highlights                                                      | . 9 |

| 2.3 MPLAB ICE 4000 System Components                                | . 9 |

| 2.4 Driver and Software Installation                                | 10  |

| 2.5 Hardware Setup                                                  | 11  |

| 2.6 Applying Power to the System Components                         | 12  |

| 2.7 Applying Power to the System Components – Low Voltage Emulation | 12  |

| 2.8 Software Setup                                                  | 13  |

| 2.9 Removing Power From the System Components                       | 14  |

| Chapter 3. General Set Up                                           |     |

| 3.1 Introduction                                                    | 15  |

| 3.2 Highlights                                                      | 15  |

| 3.3 Checking Configuration Bit Values                               | 15  |

| 3.4 Configuring the Communications Port                             | 16  |

| 3.5 Selecting Processor Power                                       | 16  |

| 3.6 Setting Up the Processor Clock                                  | 17  |

| 3.7 Setting Up Miscellaneous Hardware                               | 18  |

| 3.8 Using MPLAB IDE Projects and Work Spaces                        | 19  |

| Chapter 4. Basic Features                                           |     |

| 4.1 Introduction                                                    | 21  |

| 4.2 Highlights                                                      | 21  |

| 4.3 Starting and Stopping Emulation                                 | 21  |

| 4.4 Viewing Processor Memory and Files                              | 22  |

| 4.5 Using Software Breakpoints                                      | 22  |

| 4.6 Using Hardware Breakpoints                                      | 23  |

| 4.7 Using Trigger In/Out Settings                                   | 23  |

| 4.8 Using a Real-Time Watch                                         | 24  |

| 4.9 Using the Stopwatch                                             | 25  |

| 4.10 Monitoring Emulator States and Operations                      | 25  |

| Chapter 5. External Memory Usage                        |    |

|---------------------------------------------------------|----|

| 5.1 Introduction                                        | 27 |

| 5.2 Highlights                                          | 27 |

| 5.3 PIC18F8XXX Program Memory Modes                     | 27 |

| 5.4 Emulating PIC18F8XXX Program Memory Modes           | 29 |

| 5.5 MPLAB IDE and External Memory                       | 31 |

| Chapter 6. Complex and Internal Triggers                |    |

| 6.1 Introduction                                        | 33 |

| 6.2 Highlights                                          | 33 |

| 6.3 Complex Triggers                                    | 33 |

| 6.4 Complex Trigger Settings                            | 33 |

| 6.5 Complex Trigger Settings Syntax                     | 36 |

| 6.6 Trigger Type Selection                              | 37 |

| 6.7 Memory Selection                                    | 43 |

| 6.8 Complex Triggering Examples                         | 44 |

| 6.9 Internal Triggers                                   | 48 |

| Chapter 7. Code Coverage, Trace Memory, Real-Time Reads |    |

| 7.1 Introduction                                        | 51 |

| 7.2 Highlights                                          | 51 |

| 7.3 Code Coverage                                       | 51 |

| 7.4 Trace Memory                                        | 53 |

| 7.5 Real-Time Reads                                     | 56 |

| Chapter 8. Emulator Function Summary                    |    |

| 8.1 Introduction                                        | 57 |

| 8.2 Highlights                                          | 57 |

| 8.3 Debugger Menu                                       | 58 |

| 8.4 View Menu                                           | 59 |

| 8.5 Right Mouse Button Menu                             | 59 |

| 8.6 Toolbars                                            | 60 |

| 8.7 Status Bar                                          | 60 |

| 8.8 Additional Commands Dialog, Data Fill Tab           | 60 |

| 8.9 Additional Commands Dialog, Force Opcode Tab        | 60 |

| 8.10 Settings Dialog, Port Tab                          | 61 |

| 8.11 Settings Dialog, Info Tab                          | 61 |

| 8.12 Settings Dialog, Limitations Tab                   | 61 |

| 8.13 Settings Dialog, View Tab                          | 62 |

| 8.14 Settings Dialog, Clock Tab                         | 62 |

| 8.15 Settings Dialog, Power Tab                         | 64 |

| 8.16 Settings Dialog, Break Options Tab                 |    |

| 8.17 Settings Dialog, Memory Tab                        |    |

| 8.18 Settings Dialog, Pins/Pins and Usage Tab           | 67 |

| 8.19 Settings Dialog, Peripheral Tab                    |    |

| 8.20 Other Dialogs/Windows                              | 68 |

| Appendix A. Troubleshooting              |    |

|------------------------------------------|----|

| A.1 Introduction                         | 69 |

| A.2 Highlights                           | 69 |

| A.3 Common Problems/FAQ                  | 69 |

| A.4 Error Messages                       | 71 |

| A.5 Limitations                          | 72 |

| Appendix B. Pod Electrical Specification |    |

| B.1 Introduction                         | 73 |

| B.2 Highlights                           | 73 |

| B.3 Declaration of Conformity            | 73 |

| B.4 Power                                | 74 |

| B.5 USB Port                             | 74 |

| B.6 Indicator Lights                     | 74 |

| B.7 Logic Probes                         | 76 |

| Glossary                                 | 77 |

| Index                                    |    |

| Worldwide Sales and Service              | 92 |

NOTES:

# Preface

# INTRODUCTION

The general information discussed here can help you when using the MPLAB ICE 4000 emulator. Items discussed in this chapter include:

- About This Guide

- Warranty Registration

- Recommended Reading

- Troubleshooting

- The Microchip Web Site

- Development Systems Customer Change Notification Service

- Customer Support

#### **ABOUT THIS GUIDE**

#### **Document Layout**

This document describes how to use MPLAB ICE 4000 as a development tool to emulate and debug firmware on a target board. The manual layout is as follows:

- **Chapter 1: Overview** What MPLAB ICE 4000 is and how it can help you develop your application.

- Chapter 2: Installation How to install MPLAB ICE 4000 hardware and MPLAB IDE v6.xx software.

- Chapter 3: General Set Up Setting up MPLAB ICE 4000 for use with MPLAB IDE.

- Chapter 4: Basic Features A description of the basic features of MPLAB ICE 4000, (i.e., run, halt, reset, single step, etc.).

- Chapter 5: External Memory Usage A description of PIC18F8XXX external memory modes and how they are supported on the emulator.

- Chapter 6: Complex and Internal Triggers A description of complex triggers and dsPIC<sup>®</sup> internal triggers. Complex trigger examples are also given.

- Chapter 7: Code Coverage, Trace Memory, Real-Time Reads A description of code coverage, emulator trace and real-time reads.

- Chapter 8: Emulator Function Summary A summary of emulator functions available in MPLAB IDE when MPLAB ICE 4000 is chosen as the debug tool.

- Appendix A: Troubleshooting How to solve common problems with MPLAB ICE 4000 operation.

- Appendix B: Pod Electrical Specification The electrical specifications and description of the emulator pod.

- Glossary A glossary of terms used.

# **Conventions Used in this Guide**

This manual uses the following documentation conventions: **DOCUMENTATION CONVENTIONS**

| Description                                 | Represents                                                                                                                       | Examples                                                            |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| Main Document (Arial for                    | ont):                                                                                                                            | I                                                                   |  |

| Italic characters                           | Referenced books                                                                                                                 | MPLAB IDE User's Guide                                              |  |

|                                             | Emphasized text                                                                                                                  | is the only compiler                                                |  |

| Interface References (A                     | rial font):                                                                                                                      |                                                                     |  |

| Initial caps                                | A window, dialog or menu selection                                                                                               | Configuration Bits window,<br>Settings dialog, Enable<br>Programmer |  |

| Quotes                                      | A field name in a window or dialog                                                                                               | "Save files before running the debugger"                            |  |

| Underlined, italic text<br>with right arrow | A menu selection path                                                                                                            | <u>File&gt;Save</u>                                                 |  |

| Bold characters                             | A dialog button or tab                                                                                                           | OK button, Power tab                                                |  |

| Characters in angle<br>brackets < >         | A key on the keyboard                                                                                                            | <tab>, <ctrl-c></ctrl-c></tab>                                      |  |

| Code References (Cour                       | ier font):                                                                                                                       |                                                                     |  |

| Plain characters                            | File names and paths                                                                                                             | c:\autoexec.bat                                                     |  |

|                                             | Bit values                                                                                                                       | 0, 1                                                                |  |

|                                             | Sample code                                                                                                                      | #define START                                                       |  |

| Square brackets []                          | Optional arguments                                                                                                               | mpasmwin [main.asm]                                                 |  |

| Curly brackets and pipe character: {   }    | Choice of mutually exclusive argu-<br>ments<br>An OR selection                                                                   | errorlevel {0 1}                                                    |  |

| Italic characters                           | A variable argument; it can be either a type of data (in lower case characters) or a specific example (in uppercase characters). | ase characters)                                                     |  |

| Ellipses                                    | Replaces repeated instances of text                                                                                              | <pre>list ["list_option, "list_option"]</pre>                       |  |

| 0xnnnn                                      | A hexadecimal number where <i>n</i> is a hexadecimal digit                                                                       | 0xFFFF, 0x007A, 0x1A                                                |  |

| ʻb <i>nnnn</i>                              | A binary number where <i>n</i> is a digit                                                                                        | ʻb00100, ʻb10                                                       |  |

# **Documentation Updates**

All documentation becomes dated, and this user's guide is no exception. Since Microchip tools and documentation are constantly evolving to meet customer needs, some actual dialogs and/or tool descriptions may differ from those in this document. Please refer to our web site to obtain the latest documentation available.

#### **Documentation Numbering Conventions**

Documents are identified with a "DS" number. This number is located on the bottom of each page, in front of the page number. The numbering convention for the DS Number is: DSXXXXXA;

where:

А

XXXXX = The document number.

= The revision level of the document.

### WARRANTY REGISTRATION

Please complete the enclosed Warranty Registration Card and mail it promptly. Sending in your Warranty Registration Card entitles you to receive new product updates. Interim software releases are available at the Microchip web site.

#### **RECOMMENDED READING**

This user's guide describes how to use MPLAB ICE 4000. Other useful documents are listed below. The following Microchip documents are available and recommended as supplemental reference resources.

#### Readme for MPLAB ICE 4000

For the latest information on using MPLAB ICE 4000, read the "Readme for MPLAB ICE 4000.txt" file (an ASCII text file) in the Readmes subdirectory of the MPLAB IDE installation directory. The Readme file contains update information and known issues that may not be included in this user's guide.

#### **Readme Files**

For the latest information on using other tools, read the tool-specific Readme files in the Readmes subdirectory of the MPLAB IDE installation directory. The Readme files contain update information and known issues that may not be included in this user's guide.

#### MPLAB ICE 4000 Processor Module and Device Adapter Specification (DS51298)

Consult this document for information on the different processor modules and device adaptors available for use with the MPLAB ICE 4000 pod.

#### MPLAB ICE Transition Socket Specification (DS51194)

Consult this document for information on transition sockets available for use with MPLAB ICE 2000/4000 device adaptors.

#### TROUBLESHOOTING

See Appendix A. "Troubleshooting" for information on common problems.

# THE MICROCHIP WEB SITE

Microchip provides online support on the Microchip World Wide Web (WWW) site. The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, you must have access to the Internet and a web browser such as Netscape<sup>®</sup> Navigator or Microsoft<sup>®</sup> Internet Explorer.

The Microchip web site is available by using your favorite Internet browser:

www.microchip.com

The web site provides a variety of services. Users may download files for the latest development tools, data sheets, application notes, user's guides, articles and sample programs. A variety of information specific to the business of Microchip is also available, including listings of Microchip sales offices, distributors and factory representatives.

#### **Technical Support**

- Frequently Asked Questions (FAQ)

- Online Discussion Groups Conferences for products, Development Systems, technical information and more

- Microchip Consultant Program Member Listing

- · Links to other useful web sites related to Microchip products

#### **Product/Design Support**

- Design Tips

- Device Errata

#### Other available information

- Latest Microchip Press Releases

- Listing of seminars and events

- Job Postings

- Investor Information

# DEVELOPMENT SYSTEMS CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip started the customer notification service to help our customers keep current on Microchip products with the least amount of effort. Once you subscribe, you will receive email notification whenever we change, update, revise or have errata related to your specified product family or development tool of interest.

Go to the Microchip web page (www.microchip.com) and click on Customer Change Notification under Support. Follow the instructions to register.

The Development Systems product group categories are:

- Compilers The latest information on Microchip C compilers and other language tools. These include the MPLAB C18 and MPLAB C30 C compilers; MPASM and MPLAB ASM30 assemblers; MPLINK and MPLAB LINK30 object linkers; and MPLIB and MPLAB LIB30 object librarians.

- **Emulators** The latest information on Microchip in-circuit emulators. This includes the MPLAB ICE 2000 and MPLAB ICE 4000.

- In-Circuit Debuggers The latest information on the Microchip in-circuit debugger, MPLAB ICD 2.

- **MPLAB IDE** The latest information on Microchip MPLAB IDE, the Windows<sup>®</sup> Integrated Development Environment for development systems tools. This list is focused on the MPLAB IDE, MPLAB SIM simulator, MPLAB IDE Project Manager and general editing and debugging features.

- Programmers The latest information on Microchip programmers. These include the MPLAB ICD 2, PRO MATE II and MPLAB PM3 device programmers and the PICSTART Plus development programmer.

# **CUSTOMER SUPPORT**

Microchip customers can receive assistance through several channels.

#### Hotline

There is a Systems Information and Upgrade Line. This line provides customers a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.

The Hotline Numbers are:

1-800-755-2345 for U.S. and most of Canada.

1-480-792-7302 for the rest of the world.

#### In The Field

Customers should call their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. See the back cover for a listing of sales offices and locations.

#### **Corporate Applications**

Corporate Applications Engineers (CAEs) may be contacted at (480) 792-7627. You will need an active internet connection to obtain a "ticket" for assistance.

NOTES:

# MPLAB<sup>®</sup> ICE 4000 USER'S GUIDE

# **Chapter 1. Overview**

# 1.1 INTRODUCTION

An overview of the MPLAB ICE 4000 system is given.

# 1.2 HIGHLIGHTS

This chapter discusses:

- MPLAB ICE 4000 Defined

- How MPLAB ICE 4000 Helps You

- MPLAB ICE 4000 Kit Components

# 1.3 MPLAB ICE 4000 DEFINED

MPLAB ICE 4000 is an In-Circuit Emulator (ICE) designed to emulate PIC18X microcontroller (MCU) devices and dsPIC digital signal controller (DSC) devices. It uses the latest emulation processors to provide full-speed emulation and visibility into both the instruction and the data paths during execution.

MPLAB ICE 4000 performs basic functions such as run, halt, single step, and software breakpoints, plus advanced features such as instruction address data monitoring, instruction data trace, complex triggering and code coverage, and extended memory access.

MPLAB ICE 4000 support is integrated into MPLAB IDE v6.xx, Microchip's 32-bit Integrated Development Environment (IDE). The MPLAB IDE desktop provides an environment for developing and debugging your application.

This document covers the basic setup and operation of the MPLAB ICE 4000 emulator, but it does not cover all functions of MPLAB IDE. Refer to the *MPLAB IDE v6.xx Quick Start* (DS51281) and the on-line help for MPLAB IDE v6.xx to get a full understanding of the features and debug capabilities of the MPLAB IDE.

# 1.4 HOW MPLAB ICE 4000 HELPS YOU

MPLAB ICE 4000 allows you to:

- Debug your application on your own hardware in real time.

- Debug with both hardware and software breakpoints.

- Measure timing between events using the stopwatch or complex trigger.

- Set breakpoints based on internal and/or external signals.

- Monitor internal file registers.

- Emulate full speed (depending on the device).

- Select the oscillator source in software.

- Program the application clock speed.

- Trace data bus activity and time stamp events.

- · Set complex triggers based on program and data bus events, and external inputs.

# 1.5 MPLAB ICE 4000 KIT COMPONENTS

The components of the MPLAB ICE 4000 emulator kit are listed below.

- 1. MPLAB IDE v6.xx Quick Start (DS51281)

- 2. CD-ROM with MPLAB IDE software and on-line documentation

- 3. USB cable to connect the emulator pod to a PC

- 4. Emulator pod

- 5. Power supply and cable

- 6. Emulator stand

- 7. Processor module flex circuit cable

- 8. Logic probes

Additional hardware that may be ordered separately:

- 1. Processor module

- 2. Device adapter

- 3. Transition socket

# MPLAB<sup>®</sup> ICE 4000 USER'S GUIDE

# **Chapter 2. Installation**

# 2.1 INTRODUCTION

An overview of the MPLAB ICE 4000 system components is given, as well as an explanation of how to install the system hardware and software.

# 2.2 HIGHLIGHTS

This chapter contains:

- MPLAB ICE 4000 System Components

- Driver and Software Installation

- · Hardware Setup

- Applying Power to the System Components

- Applying Power to the System Components Low Voltage Emulation

- Software Setup

- · Removing Power From the System Components

# 2.3 MPLAB ICE 4000 SYSTEM COMPONENTS

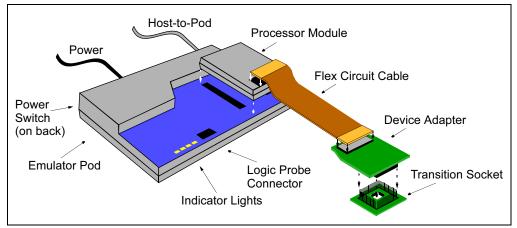

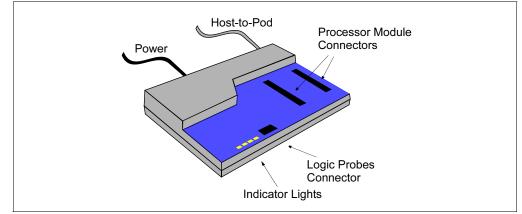

The MPLAB ICE 4000 system consists of these items (Figure 2-1):

- · Emulator pod

- Host-to-pod USB cable to connect a host PC to the emulator pod

- · Power supply cable

- Processor module

- · Flex circuit cable to connect the processor module to the device adapter

- · Device adapter

- Transition socket to connect the device adapter to the target system

- Logic probe connector

#### FIGURE 2-1: MPLAB ICE 4000 EMULATOR SYSTEM

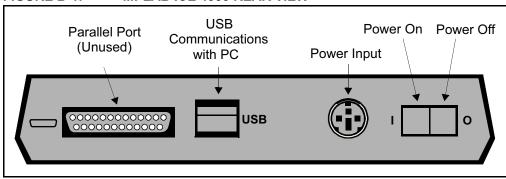

The emulator pod connects to the PC through a USB port using the provided cable. The pod contains the hardware necessary to perform the common emulator functions, such as trace, break and emulate.

The processor module inserts into two slots on top of the emulator pod. It contains the hardware necessary to emulate a specific device or family of devices. For more information on processor modules, see the *MPLAB ICE 4000 Processor Module and Device Adapter Specification* (DS51298).

The device adapter is connected to the processor module by the flex circuit cable. Device adapters are interchangeable assemblies that allow the emulator to interface to a target application system. Device adapters also have control logic that allows the target application to provide a clock source and power to the processor module. For more information on processor modules, see the *MPLAB ICE 4000 Processor Module and Device Adapter Specification* (DS51298).

The transition socket is connected to the device adapter. Transition sockets are available in various styles to allow a common device adapter to be connected to one of the supported surface mount package styles. For more information on transition sockets, see the *MPLAB ICE Transition Socket Specification* (DS51194).

The logic probes may be connected into the logic probe connector on the emulator pod.

# 2.4 DRIVER AND SOFTWARE INSTALLATION

| <b>Do not allow Windows<sup>®</sup> OS to pick a communications driver</b> ,<br>i.e., the emulator will not work and you will then have to uninstall the Windows<br>driver so you may install the proper Microchip driver.<br>If you have allowed the Windows driver to install, follow the directions in the file<br>MPUsbClean.htm found in the Drivers <i>nn</i> \ICE4k_USB subdirectory of the MPLAB IDE<br>installation directory, where <i>nn</i> is the version of Windows OS. Then return here to<br>install the correct driver. | CAUTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | i.e., the emulator will not work and you will then have to uninstall the Windows<br>driver so you may install the proper Microchip driver.<br>If you have allowed the Windows driver to install, follow the directions in the file<br>MPUsbClean.htm found in the Drivers <i>nn</i> \ICE4k_USB subdirectory of the MPLAB IDE<br>installation directory, where <i>nn</i> is the version of Windows OS. Then return here to |

- Run the installation for the MPLAB IDE v6.xx software application on your PC. You may obtain the installation executable from the Microchip web site or from the MPLAB IDE CD-ROM available from Microchip.

- 2. When the MPLAB IDE installation is complete, the driver installation instructions will appear, as well as a dialog that asks you to reboot. Click **Cancel** in the dialog and follow the driver installation instructions.

If you accidentally close these instructions, they may be found at:

MPLAB IDE installation directory\Driversnn\ICE4k\_USB\Ddice4knn.htm

where *nn* represents the version of Windows OS.

3. Shut down your PC from the Start menu.

# 2.5 HARDWARE SETUP

The PC, MPLAB ICE 4000 and the target system should NOT be powered at this time.

1. Plug the host-to-pod USB cable into the PC and then the pod.

Connect one end of the host-to-pod cable to the USB port on the PC chassis and connect the other end to the USB connector on the back of the MPLAB ICE 4000 pod.

2. Plug the power cord into the pod.

Make certain that the emulator pod on/off switch is in the "O" or "off" position before completing this step.

**Note:** USB cannot power the emulator pod, i.e., MPLAB ICE 4000 must be run with the supplied external power supply.

- 3. Plug the power cord into an outlet.

- 4. Plug the processor module into the emulator pod.

Insert the processor module firmly onto the top of the MPLAB ICE 4000 pod.

- 5. If a target board will be used with the MPLAB ICE 4000 system:

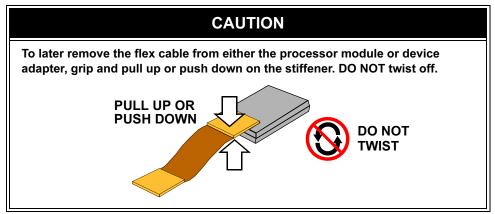

- a) Connect the end of the flex circuit cable marked "emulation module" to the processor module.

- b) Connect the end of the flex circuit cable marked "device adapter" to the device adapter.

- c) Plug the device adapter into the transition socket on your target application. Make sure the target application powers the transition socket according the electrical specs for the device to be emulated.

- d) Connect the logic probes. Plug the logic probes into the logic probe connector found on the front of the emulator pod.

# 2.6 APPLYING POWER TO THE SYSTEM COMPONENTS

To prevent damage to any of the subsystem or target application parts, power up the system components as specified below.

# CAUTION

Damage to the emulator system and/or target application may occur if these steps are not followed.

**Note:** When power is supplied by the target system, MPLAB ICE 4000 loads the target system with up to 150 mA. An MPLAB ICE 4000 device adapter loads the system with up to 10 mA.

See Section 2.7 "Applying Power to the System Components – Low Voltage Emulation" before using low voltage emulation if this feature is desired.

- 1. Apply power to the PC.

- 2. Apply power to the emulator pod.

#### CAUTION

Insert the processor module BEFORE turning on the emulator pod. DO NOT insert a processor module with power applied to the pod.

3. Apply power to the target application circuit.

# 2.7 APPLYING POWER TO THE SYSTEM COMPONENTS – LOW VOLTAGE EMULATION

MPLAB ICE 4000 supports low voltage emulation (2.5V). In this configuration, **power MUST BE SUPPLIED by the target system**.

**Note:** When power is supplied by the target system, MPLAB ICE 4000 loads the target system with up to 150 mA. An MPLAB ICE 4000 device adapter loads the system with up to 10 mA.

To prevent damage to any of the subsystem or target application parts, power up the system components as specified below.

# CAUTION

Damage to the emulator system and/or target application may occur if these steps are not followed.

- 1. Check the limitations for your selected device. Some devices allow emulator pins to come up as output high, instead of input. Make certain you do not allow the emulated device to do this if your application cannot tolerate 5V.

- 2. Apply power to the PC.

- 3. Apply power to the emulator pod.

# CAUTION

Insert the processor module BEFORE turning on the emulator pod. DO NOT insert a processor module with power applied to the pod.

4. Apply power to the target application circuit.

# 2.8 SOFTWARE SETUP

- 1. Launch MPLAB IDE v6.xx.

- 2. From the Configure menu, select Select Device. In this dialog, choose the device you will be emulating and click **OK**.

- 3. From the Debugger menu, select Select Tool and then MPLAB ICE 4000 to enable the emulator.

**Note:** If you cannot select the emulator as the debug tool, please see **Appendix A. "Troubleshooting"**.

Once you have selected MPLAB ICE 4000, debug options will appear on the Debugger menu.

**Note:** It is recommended that you **not** have a programmer enabled at the same time as the emulator. See **Appendix A. "Troubleshooting"** for more information.

- The default port setting is USB = ICEUSB-0. If you wish to change this settings, you may do so on the Port tab of the <u>Debugger>Settings</u> dialog. See Section 3.4 "Configuring the Communications Port" for more information.

- 5. MPLAB ICE 4000 allows the emulator processor module to be powered by either the emulator pod or the target system. This is set up in MPLAB IDE as follows:

- Emulator pod: <u>Debugger>Settings</u>, **Power** tab, "Processor Power From Emulator"

- Target system: <u>Debugger>Settings</u>, **Power** tab, "Processor Power From Target Board"

**Note:** You must select "Processor Power From Target Board" when using low-voltage emulation.

See **Section 3.5 "Selecting Processor Power**" for more information. Also, refer to the *MPLAB ICE 4000 Processor Module and Device Adapter Specification* for processor module power requirements before configuring the system for target system power.

When connecting to a target application system, you may notice a voltage level on the target application, even though you have not yet applied power to the target application circuit. This is normal and is due to current leakage of protection diodes through Vcc of the Device Adapter. The current leakage will typically be less than 20 mA. However, if the target application is using a voltage regulator, it should be noted that some regulators require the use of an external shunt diode between VIN and VOUT for reverse-bias protection. Refer to the manufacture's data sheets for additional information.

MPLAB ICE 4000 should now be ready for you to use as an emulator. If you have had problems, please consult **Appendix A. "Troubleshooting**". Otherwise, proceed to the next chapter for additional software setup considerations.

# 2.9 REMOVING POWER FROM THE SYSTEM COMPONENTS

To prevent damage to any of the subsystem or target application parts, power down the system components as specified below.

# CAUTION

Damage to the emulator system and/or target application may occur if these steps are not followed.

- 1. Select <u>Debugger>None</u>.

- 2. Close MPLAB IDE v6.xx. Save any projects/work spaces when prompted.

- 3. Remove power from target application circuit.

- 4. Turn off the emulator pod.

- 5. Turn off the PC.

# MPLAB<sup>®</sup> ICE 4000 USER'S GUIDE

# Chapter 3. General Set Up

# 3.1 INTRODUCTION

After installing MPLAB ICE 4000 and starting up the MPLAB IDE, MPLAB IDE must be set up to correctly emulate the selected processor.

# 3.2 HIGHLIGHTS

The steps needed to get started with MPLAB ICE 4000 are:

- Checking Configuration Bit Values

- · Configuring the Communications Port

- Selecting Processor Power

- Setting Up the Processor Clock

- · Setting Up Miscellaneous Hardware

- Using MPLAB IDE Projects and Work spaces

# 3.3 CHECKING CONFIGURATION BIT VALUES

To view the values of configuration bits for your selected device, open the Configuration Bits window by selecting <u>Configure>Configuration Bits</u>.

When you first select a device and start a project, default data sheet values for configuration bits are used. These may not be what you want for development, e.g., you may not want the watchdog timer enabled.

# 3.3.1 Watchdog Timer On/Off

Determine whether or not the Watchdog Timer (WDT) will be needed. During development, WDT is usually disabled. However, if a specific development requires the WDT to be enabled, remember to set its prescaler.

#### 3.3.2 Processor Mode and External Memory

If a processor has a mode that supports external program memory (Microprocessor or Extended Microcontroller), select the mode here. Additional memory features are set up on the **Memory** tab of the Settings dialog.

PIC18C601/801 devices use external memory exclusively (they have no on-chip program memory), so there is no need for Processor mode selection bits. However, you may use the **Memory** tab to set up whether the external memory is provided by the emulator or the target.

#### 3.3.3 Oscillator Settings

Select the oscillator you will use for development here and the frequency for the oscillator in <u>Debugger>Settings</u>, Clock tab (Section 3.6 "Setting Up the Processor Clock"). Make sure you only enter frequencies that are available for the selected oscillator.

# 3.4 CONFIGURING THE COMMUNICATIONS PORT

MPLAB ICE 4000 communicates with the PC via a USB port.

- 1. Select <u>Debugger>Settings</u> and click on the Port tab.

- 2. Select a communications port, where ICEUSB-x are the available USB ports. The number of available ports will depend on the configuration of individual PC's.

**Note:** Before you change the communications port in software, make sure you have first changed it in hardware.

Click **Apply** to accept the setting in this tab of the Settings dialog.

# 3.5 SELECTING PROCESSOR POWER

MPLAB ICE 4000 allows the emulator processor chip to be powered by the emulator pod (5V) or the target system (2.5V to 5V). The emulator defaults to Processor Power from Emulator (system power) when first initialized.

For information on processor module power issues, please refer to the MPLAB ICE 4000 Processor Module and Device Adapter Specification.

#### FIGURE 3-1: SETTINGS DIALOG – POWER TAB

| Processor Power     |   |

|---------------------|---|

| From Emulator       | L |

| C From Target Board |   |

#### 3.5.1 Processor Power from Emulator (System Power)

Select the **Power** tab of the <u>Debugger>Settings</u> dialog. Under Processor Power, select From Emulator and click **Apply**.

**Note:** The emulator system cannot provide power to a target board through a device adapter. If the device adapter is plugged into an unpowered target board, it is not unusual to see a voltage level of 1-3V at Vcc of the target board, caused by leakage current through Vcc of the device adapter. MPLAB IDE may also have difficulty initializing the emulator when power has not yet been applied to the target board.

### 3.5.2 Processor Power from Target Board

Select the **Power** tab of the <u>Debugger>Settings</u> dialog. Under Processor Power, select From Target Board and click **Apply**.

Refer to the *MPLAB ICE 4000 Processor Module and Device Adapter Specification* for processor module power requirements before configuring the system for target system power.

**Note:** If you use power from the target board, make sure it is always present or the emulator will not function properly. If the device adapter is plugged into an unpowered target board, there may still be some leakage current through Vcc of the device adapter. MPLAB IDE may also have difficulty initializing the emulator when power has not yet been applied to the target board.

#### 3.5.3 Low Voltage Emulation

MPLAB ICE 4000 also supports LOW VOLTAGE emulation down to 2.5V. The emulator system cannot provide any voltage level other than 5V to the emulator processor. In this configuration, power must be supplied by the target board (see **Section 3.5.2** "**Processor Power from Target Board**").

Before using low voltage, check the limitations for your selected device. Some devices allow emulator pins to come up as output high, instead of input. Make certain you do not allow the emulated device to do this if your application cannot tolerate 5V.

# 3.6 SETTING UP THE PROCESSOR CLOCK

MPLAB ICE 4000 can use the on-board clock with either emulator or target power, or it can use the target board clock with target board power.

#### 3.6.1 Using the On-board Clock

MPLAB ICE 4000 has an on-board clock that can be programmed to a frequency between 32 kHz and 100 MHz. Refer to the specific device's data sheet to determine the supported frequency range.

- 1. Select an Oscillator Type (Section 3.3.3 "Oscillator Settings").

- 2. Select the Clock tab on the <u>Debugger>Settings</u> dialog.

- 3. Select the Desired Frequency magnitude (MHz, kHz or Hz) and enter the Desired Frequency. Refer to the specific device's data sheet to determine the supported frequency range for each oscillator type.

**Note:** If you enter a frequency that is out of range, your system will not operate properly.

#### 4. Click Apply.

The clock will be programmed to operate as close to the entered frequency as possible. Since the generated clock frequency will be slightly different than the desired clock frequency, the Actual Frequency will be displayed. The Actual Frequency will be within 0.5% of the desired frequency.

#### 3.6.1.1 PLL

If the Oscillator mode has a HW PLL associated with it, the run time frequency will be the desired frequency. Example: To emulate a target with a 5 MHz HS crystal while using HW PLL mode, set the desired frequency to 20 MHz.

For parts (e.g., PIC18F8680) that support SW enabled PLL, please do not enter a frequency that, when multiplied by 4, would go over the maximum speed the emulator supports.

Consult the device limitations to see how PLL is emulated for your selected device.

#### 3.6.1.2 VERIFY FREQUENCY

To verify the clock frequency, you can set up a complex trigger and then measure the trigger output pulse width (one instruction cycle) of the TRIGOUT logic probe (Section B.7 "Logic Probes") in frequency and multiply by 4.

# 3.6.2 Using a Target Board Clock

MPLAB ICE 4000 can use the processor clock on the target board as long as target board (external) power is being used. It can determine the frequency of the target board clock and use it for displaying timing information.

- 1. Select the target board Oscillator Type (Section 3.3.3 "Oscillator Settings").

- Select the Power tab of the <u>Debugger>Settings</u> dialog and set Processor Power to From Target Board (see Section 3.5.2 "Processor Power from Target Board").

- Select the Clock tab on the <u>Debugger>Settings</u> dialog. Then select Use Target Board Clock.

**Note:** If MPLAB ICE 4000 is not hooked up to a target board and you click **Use Target Board Clock**, you will get a warning dialog.

The target board clock frequency will be calculated, displayed and used for any internal time calculations. A warning is issued if the frequency is less than 32 kHz.

Because of measurement error, the calculated frequency may not be what is desired for internal time calculations. (e.g., Your crystal oscillator has a frequency of 8 MHz  $\pm$  50 ppm, but the target frequency is shown as 7.993755.) Measurement error can range from 3.9% to a fraction of a percent.

4. Click Apply.

# 3.7 SETTING UP MISCELLANEOUS HARDWARE

In addition to the settings you have already made, there are other settings that you may or may not wish to change in the <u>Debugger>Settings</u> dialog. Depending on the device you have chosen, these tabs may or may not be available and may look different for different devices.

#### 3.7.1 Settings Dialog, Break Options Tab

Use the Break Options tab to change the global break and trace point environment options. These include Global Hardware Break Enable (for complex trigger usage) and Freeze Peripherals on Halt. If enabled in the configuration bits (<u>Configure>Configuration Bits</u>), you may set stack and watchdog timer break options.

# 3.7.2 Settings Dialog, Memory Tab

Some parts allow device memory to be supplemented or replaced by off-chip (external) memory. Memory modes are selected using configuration bits (<u>Configure>Configuration Bits</u>).

Devices that support Microcontroller mode only do not have a Memory tab. Devices that support Extended Microcontroller mode and/or Microprocessor mode will display the Memory tab.

**Note:** There are several limitations concerning external memory, some of them device-dependent. Please see the limitations section of the on-line help file for more information.

# 3.7.3 Settings Dialog, Pins Tab

Set up processor pins, such as the MCLR pull-up resistor connection. Also set up the emulator operation to preserve user's external bus access method when halted.

#### 3.7.4 Settings Dialog, Peripheral Tab

Set up peripheral functions, such a freeze on halt.

# 3.8 USING MPLAB IDE PROJECTS AND WORK SPACES

MPLAB IDE v5.xx and lower used projects to help you manage the files to build your application. MPLAB IDE v6.xx now uses projects and work spaces to aid in the development of complicated applications.

For general information on projects and work spaces, see the on-line help for MPLAB IDE v6.xx.

NOTES:

# MPLAB<sup>®</sup> ICE 4000 USER'S GUIDE

# **Chapter 4. Basic Features**

# 4.1 INTRODUCTION

MPLAB ICE 4000 provides a wide variety of tools to emulate and debug an application. MPLAB ICE 4000 offers a basic set of in-circuit debugging tools, including the ability to run, halt, reset and single step the processor, plus additional tools for advanced debugging techniques.

Several basic MPLAB ICE 4000 emulator features are built-in to the MPLAB IDE software. A general description of these features is provided here, but for more detailed information, consult the MPLAB IDE documentation.

Other basic tools appear when MPLAB ICE 4000 is selected as the debug tool.

# 4.2 HIGHLIGHTS

MPLAB ICE 4000 basic features include the following:

- Starting and Stopping Emulation

- Viewing Processor Memory and Files

- Using Software Breakpoints

- Using Hardware Breakpoints

- Using Trigger In/Out Settings

- Using a Real-Time Watch

- Using the Stopwatch

- Monitoring Emulator States and Operations

# 4.3 STARTING AND STOPPING EMULATION

To debug an application in MPLAB IDE, you must either build your source code into an executable file using projects and work spaces (see MPLAB IDE on-line help for more information) or you must import an existing executable file using *File>Import*. Once you have your application in executable form, you may run, halt, step through or reset your code.

- To run your code, select either <u>Debugger>Run</u> or Run from the Debug toolbar.

- To halt your code, select either <u>Debugger>Halt</u> or **Halt** from the Debug toolbar.

- To step through your code, select either <u>Debugger>Step Into</u> or Step Into from the Debug toolbar. Be careful not to step into a Sleep instruction or you will have to perform a processor reset to resume emulation.

**Note:** You cannot step through external memory high-level language code in the Program Memory or File window. Use the Disassembly window.

- To step over a line of code, select either <u>Debugger>Step Over</u> or Step Over from the Debug toolbar.

- To repeatedly step through your code, select either <u>Debugger>Animate</u> or Animate from the Debug toolbar.

• To perform a processor reset on your code, select either <u>Debugger>Reset></u> <u>Processor Reset</u> or **Reset** from the Debug toolbar. Additional resets, such as POR/BOR, MCLR and System, may be available, depending on device.

Remember to rebuild your program when making changes so the code being executed accurately reflects the current state of your application.

# 4.4 VIEWING PROCESSOR MEMORY AND FILES

MPLAB IDE provides several standard windows for viewing debug and various processor memory information, selectable from the View menu. See MPLAB IDE on-line help for more information on using these windows.

- Project view the project tree

- · Output view output from build and other tools

- · Hardware Stack view the hardware stack contents

- · Program Memory view program memory contents

- File Registers view file register contents

- EEPROM view the EEPROM memory contents

- Watch view selected SFRs and symbols

- Special Function Registers view SFR contents

In addition, you may view trace results. For more on trace, see **Chapter 7. "Code Coverage, Trace Memory, Real-Time Reads"**.

ICE Trace – view the contents of the trace buffer

To view your source code, select *File>Open* and enter or browse for the source code file. Code in this window is color-coded according to the processor and build tool selected. To change the style of color-coding, click the right mouse button and select *Advanced>Text Mode*. To change the colors used, click the right mouse button and select Properties, Text tab. For information on using this window to edit your code, see MPLAB Editor on-line help.

# 4.5 USING SOFTWARE BREAKPOINTS

MPLAB ICE 4000 uses software breakpoints to halt the processor at a specific location. With a software breakpoint, execution stops before the instruction at the break location is executed.

**Note:** You cannot set software breakpoints in external Flash memory. Use the complex trigger to set hardware breakpoints. You can set software breakpoints in external RAM memory.

Some considerations when using software breakpoints:

- If a software breakpoint is set, then checksums calculated on program memory at run time will be incorrect. Programmer checksums are not affected.

- Manually resetting the time-stamp when using software breakpoints will cause the time-stamp to be incorrect.

Software breakpoints are a standard MPLAB IDE debug feature:

• MPLAB IDE Help – Using Breakpoints

# 4.6 USING HARDWARE BREAKPOINTS

In addition to setting software breakpoints on program memory addresses, hardware breakpoints may be set with more complex conditions. Also, hardware breakpoints can be used to capture real-time events.

With a hardware breakpoint, execution halt may *skid*, or one or more additional instructions may be executed past the set breakpoint before the processor halts.

Hardware breakpoints are set using the complex trigger. The complex trigger can be set up to require that up to four events occur before a break (or trace) occurs. The combination of these events can be specified three ways:

- Sequential

- All Events

- Any Event

In addition, the complex triggering feature along with the trace memory window can be used to perform the following functions:

- Time Between Events

- Filter Trace

Complex trigger breakpoints can then be selectively enabled and disabled. Breakpoints set in this manner are retained with the project.

Select <u>Debugger>Complex Triggers and Code Coverage</u> and click on the Complex Trigger Settings tab.

For more information on complex triggering, as well as complex triggering examples, see **Chapter 6. "Complex and Internal Triggers"**.

# 4.7 USING TRIGGER IN/OUT SETTINGS

MPLAB ICE 4000 offers the following external input and output options:

- Generate a single pulse of nonspecific duration, either on the final trigger event or on a filtered trace event. Use the positive edge to trigger other equipment.

- Break on a specified edge of an external trigger input.

- Freeze the trace buffer on the rising edge of the external trigger input.

These options are set through the Trigger In/Out Settings dialog (via <u>Debugger>Complex Triggers and Code Coverage</u>, Trigger In/Out Settings tab). Trigger In/Out Settings can be used with the logic probes (**Section B.7 "Logic Probes**").

| 1160KL 4-1. | TRIGGER IN/OUT SETTINGS TAB                                                                                       |            |

|-------------|-------------------------------------------------------------------------------------------------------------------|------------|

|             | MPLAB ICE 4000 Analyzer                                                                                           | <u>? ×</u> |

|             | Complex Trigger Settings Trigger In/Out Settings Code Coverage                                                    |            |

|             | <ul> <li>Trigger Out Source</li> <li>Pulsed on final trigger event</li> <li>○ Pulsed on filtered trace</li> </ul> |            |

|             | Break On External Trigger Input                                                                                   |            |

|             | Freeze trace buffer on rising edge of trigger input                                                               |            |

|             |                                                                                                                   |            |

|             |                                                                                                                   |            |

|             | OK Cancel Apply                                                                                                   | Help       |

#### FIGURE 4-1: TRIGGER IN/OUT SETTINGS TAB

# 4.7.1 Trigger Out Source (TRGOUT)

Select either "Pulsed on final trigger event" or "Pulsed on filtered trace". If you select "Pulsed on final trigger event", the pulse will only occur on the final event. If you want a repeating pulse every time an event occurs, select "Pulsed on filtered trace".

#### 4.7.2 Break On External Trigger Input (TRGIN)

Select Enable break on external trigger input, and then specify the following:

- Break on a specified rising or falling edge of an external trigger input.

- Freeze trace buffer on rising edge of trigger input (TRGIN)

Select Freeze trace buffer on rising edge of trigger input if you wish to freeze the trace buffer on the rising edge of the external trigger input.

# 4.8 USING A REAL-TIME WATCH

Watch window variables will be updated real-time if bus access (read/write) occurs that affects those variables. However, increments or decrements of the variables will not cause an updates.

For more information on watch windows, please refer to documentation for MPLAB IDE v6.xx or greater.

# 4.9 USING THE STOPWATCH

MPLAB ICE 4000 provides a stopwatch to use with emulation (see dialog below).

- System Clock The running time, in seconds, based on the PC system clock. You may reset the time immediately by clicking **Reset Now**, or on a halt by checking Clear on Reset (When Halted).

- **Processor** Displays the frequency for the selected device (Processor Frequency) in MHz versus the calculated (average) Instruction Cycle rate. For the actual instruction cycles run, see the ICE trace window.

| FIGURE 4-2: | STOPWATCH DIALOG |

|-------------|------------------|

|             |                  |

| s | opwatch                                    |

|---|--------------------------------------------|

|   | System Clock                               |

|   | Clear Now Time (nSec): 0                   |

|   | Clear on Reset (When Halted)               |

|   | Processor                                  |

|   | Processor Frequency (MHz): 4.000000        |

|   | Instruction Cycles (Calculated): 0         |

|   | (NOTE: For actual values, view ICE trace.) |

|   | Close Help                                 |

|   |                                            |

# 4.10 MONITORING EMULATOR STATES AND OPERATIONS

Select <u>Debugger>Settings</u>, View tab and click Show State and Operation Gauge to open an emulator monitor window.

| Real-Time Reads<br>PMF Voltage<br>Clock Source<br>Power Source<br>Low Voltage Function<br>Freeze Peripherals<br>Stack Full/Overflow<br>Watch Dog Timer<br>Mode | USB 0<br>Disabled<br>4.94 V<br>Emulator<br>20.000 MHz<br>Emulator<br>Disabled<br>On Halt<br>Enabled / Break<br>Disabled<br>Microcontroller (MC)<br>Supplies 0x00000000-0x0001FFF<br>Not Used | F                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Operation<br>Idle Run<br>Initialize Step<br>Read Reset<br>Write Indicator Update Speed                                                                         | Accessing<br>ICE Program Memory<br>File Registers<br>Config Memory<br>EE Data<br>Iow Fast<br>Off                                                                                             | Stack<br>Triggers<br>Code Coverage |

#### FIGURE 4-3: ICE STATE AND OPERATIONS GAUGE WINDOW

View basic emulator data in the top portion of the window. Depending on the device selected for emulation, more or less items may be displayed.

| ltem                   | Definition                                                        | Change Using                                                                                                                  |

|------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Port                   | Type of communications port<br>between the emulator and the<br>PC | <u>Debugger&gt;Settings</u> , <b>Port</b> tab                                                                                 |

| Real-Time Reads*       | Enabled or disabled                                               | <i><u>Debugger&gt;Settings</u></i> , <b>View</b> tab                                                                          |

| PMF Voltage            | Current operating voltage of the processor module                 | See Low Voltage Function                                                                                                      |

| Clock Source           | Emulator or target                                                | <u>Configure&gt;Configuration Bits,</u><br>Oscillator<br><u>Debugger&gt;Settings</u> , <b>Clock</b> tab                       |

| Frequency              | Current operating frequency                                       | <u>Configure&gt;Configuration Bits,</u><br>Oscillator<br><u>Debugger&gt;Settings</u> , <b>Clock</b> tab                       |

| Power Source           | Emulator or target                                                | <u>Debugger&gt;Settings</u> , <b>Power</b> tab                                                                                |

| Low Voltage Function*  | Enabled or disabled                                               | <u>Configure&gt;Configuration Bits,</u><br>Low Voltage Program                                                                |

| Freeze Peripherals     | On halt or Not Used                                               | <u>Debugger&gt;Settings</u> , Break<br>Options tab                                                                            |

| Stack Full/Overflow    | Enabled or disabled, break or reset                               | <u>Configure&gt;Configuration Bits,</u><br>Stack Overflow<br><u>Debugger&gt;Settings</u> , <b>Break</b><br><b>Options</b> tab |

| Watchdog Timer         | Enabled or disabled, break or reset                               | <u>Configure&gt;Configuration Bits,</u><br>Watchdog Timer<br><u>Debugger&gt;Settings</u> , <b>Break</b><br><b>Options</b> tab |

| Mode*                  | Microcontroller, Extended<br>Microcontroller or<br>Microprocessor | <u>Configure&gt;Configuration Bits</u> ,<br>Processor Mode<br><u>Debugger&gt;Settings</u> , <b>Memory</b><br>tab              |

| Emulator Memory*       | Address range                                                     | <u>Configure&gt;Configuration Bits,</u><br>Processor Mode<br><u>Debugger&gt;Settings</u> , <b>Memory</b><br>tab               |

| Target Memory*         | Address range or Not Used                                         | <u>Configure&gt;Configuration Bits,</u><br>Processor Mode<br><u>Debugger&gt;Settings</u> , <b>Memory</b><br>tab               |

| MCHP Pull-up Resistor* | On emulator or on target board                                    | <u>Debugger&gt;Settings</u> , <b>Pins</b> tab                                                                                 |

TABLE 4-1: EMULATOR DATA DEFINITIONS

\* Availability dependent on device emulated.

**Operation** and **Accessing** portions of the window will display the current operation being performed by the emulator and what, if any, memory or functions are being accessed during this operation. Items will change from gray to green (highlighted) when active.

You may select how quickly the window is updated with information using the **Indicator Update Speed** bar.

# **Chapter 5. External Memory Usage**

### 5.1 INTRODUCTION

Some Microchip devices allow the extension or replacement of program memory resources with external (off-chip) memory devices. Of these devices, the MPLAB ICE 4000 supports PIC18F8XXX devices (but not PIC17CXXX devices.)

How the emulator functions for these modes is discussed here.

# 5.2 HIGHLIGHTS

Topics covered in the chapter are:

- PIC18F8XXX Program Memory Modes

- Emulating PIC18F8XXX Program Memory Modes

- MPLAB IDE and External Memory

#### 5.3 PIC18F8XXX PROGRAM MEMORY MODES

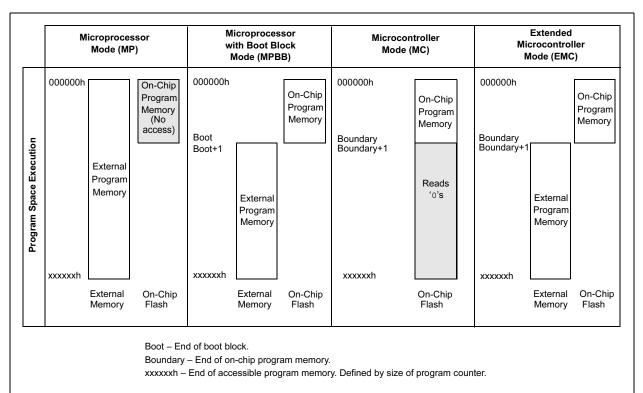

PIC18F8XXX devices are capable of operating in any one of several Program Memory modes, using combinations of on-chip and external program memory. Available Program Memory modes are as follows:

- The Microprocessor mode permits access only to external program memory; the contents of the on-chip Flash memory are ignored. The program counter permits access to a linear program memory space and defines the amount of accessible program memory (see Section 5.3.1 "Program Counter".)

- The Microprocessor with Boot Block mode accesses on-chip Flash memory from address 000000h to the end of the boot block. Above this, external program memory is accessed all the way up to the program counter accessible limit (see Section 5.3.1 "Program Counter".) Program execution automatically switches between the two memories, as required.

- The Microcontroller mode accesses only on-chip Flash memory. Attempts to read above the physical limit of the on-chip Flash causes a read of all '0's (a NOP instruction.)

- The Extended Microcontroller mode allows access to both internal and external program memories as a single block. The device can access its entire on-chip Flash memory; above this, the device accesses external program memory up to the program counter accessible limit (see Section 5.3.1 "Program Counter".) As with Boot Block mode, execution automatically switches between the two memories, as required.

In all modes, the device has complete access to data RAM and EEPROM. For more information, consult the device data sheet section "Memory Organization".

#### FIGURE 5-1: MEMORY MAPS FOR PROGRAM MEMORY MODES

5.3.1 Program Counter

The size of the program counter will determine how much program memory can be accessed, i.e., a 21-bit program counter permits access to a 2-Mbyte (1-Mword) program memory space (on-chip, off-chip or a combination of both types of program memory.)

# 5.3.2 Configuration Bits

A Program Memory mode is set by using configuration bits. Depending on the device, the Processor Mode Select bits are located in a configuration register which is programmed when the device is programmed. For more information, consult the device data sheet section "Special Features of the CPU".

#### 5.3.3 External Memory Interface

The External Memory Interface is a feature of a PIC18F8XXX device that allows the microcontroller to access external memory devices (such as Flash, EPROM, SRAM, etc.) as program or data memory.

Using the MEMCON register, the following may be configured:

- External bus enable and disable

- 16-Bit Mode Word Write mode, Byte Select mode or Byte Write mode

- Wait Table read/write bus cycle wait counts (0-3 TcY)

For more information, see the External Memory Interface section of the device data sheet.

# 5.4 EMULATING PIC18F8XXX PROGRAM MEMORY MODES

Emulating a device that uses external memory requires the following steps:

- 1. Setting Configuration Bits

- 2. Setting External Memory

- 3. Setting Memory Options

#### 5.4.1 Setting Configuration Bits

To set the values of configuration bits for your selected device, open the Configuration Bits window by selecting <u>Configure>Configuration Bits</u>. In the Category column, find Processor mode and select the mode.

**Note:** Configuration bits may also be set in code using \_\_\_\_\_config. Refer to the device data sheet and header file (.inc or .h) for more information.

#### 5.4.2 Setting External Memory

To set up MPLAB IDE and MPLAB ICE 4000 to use external memory, select <u>Configure>External Memory</u>. Then check "Use External Memory" and enter a range.

#### 5.4.3 Setting Memory Options

To set up memory options, open the Settings dialog (<u>Debugger>Settings</u>) and select the **Memory** tab (**Section 8.17 "Settings Dialog, Memory Tab"**).

The Processor mode currently selected in the configuration bits will be reflected under "Mode". If the mode selected supports external memory, functions on this tab will be active.

When emulating a Program Memory mode that makes use of external memory, two choices are available:

- External Program Memory Supplied by Emulator Use emulator memory for both on-chip and off-chip (external) memory during development. This has the advantage of speeding up program load time after a build. It has the disadvantage of not actually using the target external memory.

- External Program Memory On Target Board Use the emulator as a device would be used, with the emulator memory representing only on-chip memory. This has the advantage of testing the application as it will actually be run, with external memory. It has the disadvantage of longer upload/download times, as commands, writes and reads to external memory will take time.

In order for the MPLAB ICE 4000 to load your code into external program memory, the target system must provide SRAM or DRAM. If the target system uses non-volatile memory, such as Flash, the emulator will not be able to load code into external memory. For non-volatile memory, you must provide an alternate method of loading program memory. However, the emulator can upload non-volatile memory and run from non-volatile memory.

#### 5.4.3.1 EXTERNAL PROGRAM MEMORY SUPPLIED BY EMULATOR

To use only emulator memory, select "Supplied by Emulator" under "External (Off-Chip) Program Memory". The amount of emulator-supplied memory will display in "Emulator Supplied" under "ICE Memory Mapping". "Target Supplied" should say "Not Used".

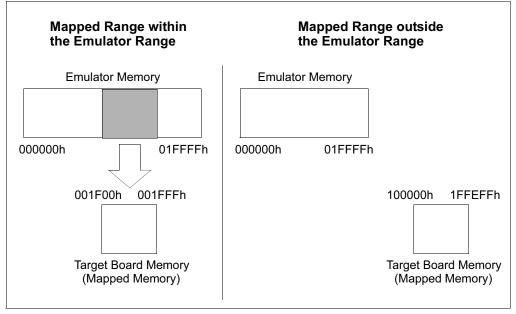

If you still need to access a range of target memory to control external circuits, set up a "Memory Mapped Peripheral Range". Check the box "Enable Banked Access Mode" and enter a target memory start and end address. This may either be a range within the emulator range, or a range above this but below the program counter maximum (see **Section 5.3.1 "Program Counter"**.)

#### FIGURE 5-2: MEMORY MAPPED PERIPHERAL RANGE

The amount of emulator- and target-supplied memory will display in "Emulator Supplied" and "Target Supplied" under "ICE Memory Mapping", respectively.

In order to communicate with the target board memory, you will need to set up the external memory interface under "Target 16-Bit Access Mode". Select the access mode (Word Write, Byte Select or Byte Write) and a table read/write Wait time in cycles. For more information, see the MEMCON register under the External Memory Interface section of the device data sheet.

#### 5.4.3.2 EXTERNAL PROGRAM MEMORY ON TARGET BOARD

To use a combination of emulator and target memory, or all target memory, select "On Target Board" under "External (Off-Chip) Program Memory". The amount of emulatorand target-supplied memory will display in "Emulator Supplied" and "Target Supplied" under "ICE Memory Mapping", respectively.

In order to communicate with the target board memory, you will need to set up the external memory interface under "Target 16-Bit Access Mode". Select the access mode (Word Write, Byte Select or Byte Write) and a table read/write Wait time in cycles. For more information, see the MEMCON register under the External Memory Interface section of the device data sheet.

#### 5.4.3.3 PIC18C601/801 CHIP SELECT SETUP

For PIC18C601/801 devices, you should specify values for the CSEL2 and CSELIO registers. See the device data sheet for more on these registers.

### 5.5 MPLAB IDE AND EXTERNAL MEMORY

Using External Memory modes with MPLAB ICE 4000 will impact the following features of MPLAB IDE.

### 5.5.1 Viewing Program Memory

To view the program memory, select <u>View>Program Memory</u>. The data for emulator program memory is always displayed. The data for external (target board) memory will be displayed as long as "Use External Memory" has been specified in the External Memory dialog (<u>Configure>External Memory</u>). To refresh the external memory display, select <u>Debugger>Upload Program Memory from ICE</u> after you run, single step or trace. If uploading takes too long, you may wish to change the amount of external memory used in the External Memory dialog.

### 5.5.2 Stepping Through Code

If your external Flash memory contains code that is written in a high-level language, such as C, you cannot step through this code using the File (Editor) window. You must use the Program Memory window.

### 5.5.3 Setting Breakpoints

Software breakpoints may be set for emulator memory or external RAM memory. Hardware breakpoints, set using the complex trigger, may be used for either emulator or any type of external memory. NOTES:

# Chapter 6. Complex and Internal Triggers

### 6.1 INTRODUCTION

In addition to the break and trigger functions discussed in **Chapter 4. "Basic Features"**, MPLAB ICE 4000 has more advanced triggering features. These include complex triggers for all devices and internal triggers for dsPIC devices.

### 6.2 HIGHLIGHTS

This chapter covers:

- · Complex Triggers

- Internal Triggers

### 6.3 COMPLEX TRIGGERS

MPLAB ICE 4000 has a highly flexible and powerful triggering mechanism. A trigger is a combination of events that can cause:

- · a hardware breakpoint, and/or

- a trace memory capture.

An event is a description of the state of the system captured during one cycle.

In addition, an external signal can be generated when the trigger occurs. This is useful for synchronizing other analyzers or equipment to MPLAB ICE 4000.

Complex trigger functions may be set using the Complex Trigger Settings tab of the MPLAB ICE 4000 Analyzer dialog.

**Note:** You must enable the Global Hardware Break Enable (<u>Debugger>Settings</u>, Break Options tab) to use complex triggering.

- Complex Trigger Settings

- Complex Trigger Settings Syntax

- Trigger Type Selection

- Memory Selection

- · Complex Triggering Examples

### 6.4 COMPLEX TRIGGER SETTINGS

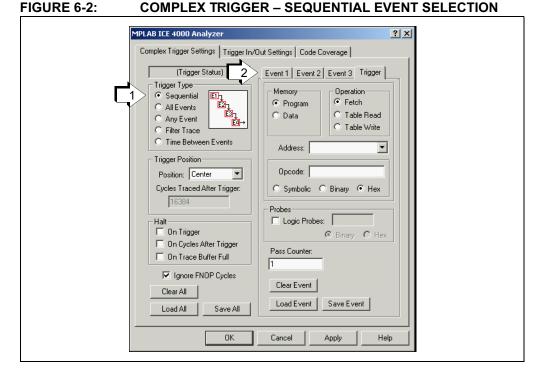

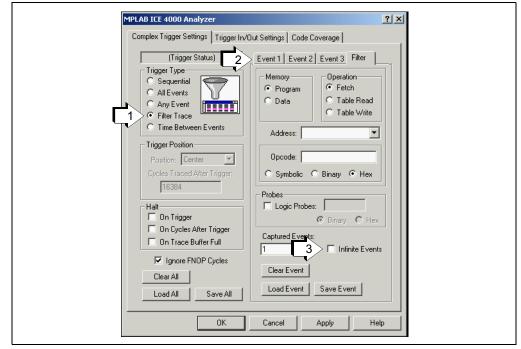

Complex triggers can be specified by selecting <u>Debugger>Complex Triggers and Code</u> <u>Coverage</u>, Complex Trigger Settings tab. The Complex Trigger Settings tab will contain different items depending on your selection of:

- 1. Trigger Type Sequential, All Events, Any Event, Time Between Events or Filter Trace

- 2. Memory Program Memory or Data Memory

Figure 6-1 shows what the tab will look like for a sequential event and program memory selection. This is the typical layout of the Complex Trigger Settings tab.

| Trigger Position<br>Position: Center                                                                                                              | Address:                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Cycles Traced After Trigger:<br>16384<br>Halt<br>On Trigger<br>On Cycles After Trigger<br>On Trace Buffer Full<br>Ignore FNOP Cycles<br>Clear All | C Symbolic O Binary O Hex<br>Probes<br>Logic Probes:<br>O Binary O Hex<br>Pass Counter:<br>1<br>Clear Event<br>Load Event<br>Save Event |

#### FIGURE 6-1: COMPLEX TRIGGER – PROGRAM MEMORY, SEQUENTIAL

For information on trigger type (event) selection, see **Section 6.6 "Trigger Type Selection"**.

Trace-related trigger information may be entered in the following items: